Loading...

Searching...

No Matches

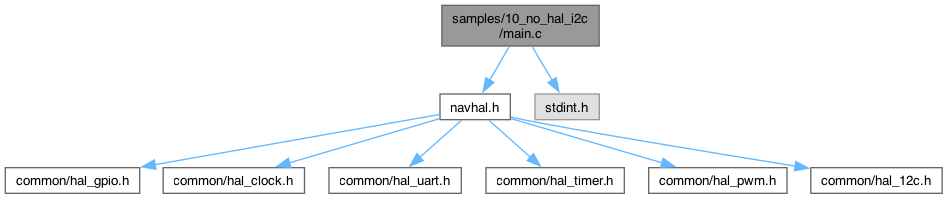

main.c File Reference

Include dependency graph for main.c:

Macros | |

| #define | CORTEX_M4 |

| #define | PERIPH_BASE 0x40000000UL |

| #define | AHB1PERIPH_BASE (PERIPH_BASE + 0x00020000UL) |

| #define | APB1PERIPH_BASE (PERIPH_BASE + 0x00000000UL) |

| #define | RCC_BASE (AHB1PERIPH_BASE + 0x3800UL) |

| #define | GPIOB_BASE (AHB1PERIPH_BASE + 0x0400UL) |

| #define | I2C1_BASE (APB1PERIPH_BASE + 0x5400UL) |

| #define | RCC_AHB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x30)) |

| #define | RCC_APB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x40)) |

| #define | GPIOB_MODER (*(volatile uint32_t *)(GPIOB_BASE + 0x00)) |

| #define | GPIOB_OTYPER (*(volatile uint32_t *)(GPIOB_BASE + 0x04)) |

| #define | GPIOB_OSPEEDR (*(volatile uint32_t *)(GPIOB_BASE + 0x08)) |

| #define | GPIOB_PUPDR (*(volatile uint32_t *)(GPIOB_BASE + 0x0C)) |

| #define | GPIOB_AFRH (*(volatile uint32_t *)(GPIOB_BASE + 0x24)) |

| #define | I2C1_CR1 (*(volatile uint32_t *)(I2C1_BASE + 0x00)) |

| #define | I2C1_CR2 (*(volatile uint32_t *)(I2C1_BASE + 0x04)) |

| #define | I2C1_OAR1 (*(volatile uint32_t *)(I2C1_BASE + 0x08)) |

| #define | I2C1_DR (*(volatile uint32_t *)(I2C1_BASE + 0x10)) |

| #define | I2C1_SR1 (*(volatile uint32_t *)(I2C1_BASE + 0x14)) |

| #define | I2C1_SR2 (*(volatile uint32_t *)(I2C1_BASE + 0x18)) |

| #define | I2C1_CCR (*(volatile uint32_t *)(I2C1_BASE + 0x1C)) |

| #define | I2C1_TRISE (*(volatile uint32_t *)(I2C1_BASE + 0x20)) |

| #define | BMP180_ADDR 0x77 |

| #define | TIMEOUT 1000000 |

Functions | |

| int | wait_flag (volatile uint32_t *reg, uint32_t mask) |

| void | uart2_write_hex (uint8_t val) |

| void | uart2_write_uint16 (uint16_t val) |

| void | i2c1_init (void) |

| void | i2c1_start (void) |

| void | i2c1_stop (void) |

| void | i2c1_write_addr (uint8_t addr) |

| void | i2c1_write_data (uint8_t data) |

| uint8_t | i2c1_read_data_nack (void) |

| uint8_t | bmp180_read_reg (uint8_t reg) |

| uint16_t | bmp180_read_u16 (uint8_t reg) |

| void | bmp180_write_reg (uint8_t reg, uint8_t value) |

| int | main (void) |

Macro Definition Documentation

◆ AHB1PERIPH_BASE

| #define AHB1PERIPH_BASE (PERIPH_BASE + 0x00020000UL) |

◆ APB1PERIPH_BASE

| #define APB1PERIPH_BASE (PERIPH_BASE + 0x00000000UL) |

◆ BMP180_ADDR

| #define BMP180_ADDR 0x77 |

◆ CORTEX_M4

| #define CORTEX_M4 |

◆ GPIOB_AFRH

| #define GPIOB_AFRH (*(volatile uint32_t *)(GPIOB_BASE + 0x24)) |

◆ GPIOB_BASE

| #define GPIOB_BASE (AHB1PERIPH_BASE + 0x0400UL) |

◆ GPIOB_MODER

| #define GPIOB_MODER (*(volatile uint32_t *)(GPIOB_BASE + 0x00)) |

◆ GPIOB_OSPEEDR

| #define GPIOB_OSPEEDR (*(volatile uint32_t *)(GPIOB_BASE + 0x08)) |

◆ GPIOB_OTYPER

| #define GPIOB_OTYPER (*(volatile uint32_t *)(GPIOB_BASE + 0x04)) |

◆ GPIOB_PUPDR

| #define GPIOB_PUPDR (*(volatile uint32_t *)(GPIOB_BASE + 0x0C)) |

◆ I2C1_BASE

| #define I2C1_BASE (APB1PERIPH_BASE + 0x5400UL) |

◆ I2C1_CCR

| #define I2C1_CCR (*(volatile uint32_t *)(I2C1_BASE + 0x1C)) |

◆ I2C1_CR1

| #define I2C1_CR1 (*(volatile uint32_t *)(I2C1_BASE + 0x00)) |

◆ I2C1_CR2

| #define I2C1_CR2 (*(volatile uint32_t *)(I2C1_BASE + 0x04)) |

◆ I2C1_DR

| #define I2C1_DR (*(volatile uint32_t *)(I2C1_BASE + 0x10)) |

◆ I2C1_OAR1

| #define I2C1_OAR1 (*(volatile uint32_t *)(I2C1_BASE + 0x08)) |

◆ I2C1_SR1

| #define I2C1_SR1 (*(volatile uint32_t *)(I2C1_BASE + 0x14)) |

◆ I2C1_SR2

| #define I2C1_SR2 (*(volatile uint32_t *)(I2C1_BASE + 0x18)) |

◆ I2C1_TRISE

| #define I2C1_TRISE (*(volatile uint32_t *)(I2C1_BASE + 0x20)) |

◆ PERIPH_BASE

| #define PERIPH_BASE 0x40000000UL |

◆ RCC_AHB1ENR

| #define RCC_AHB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x30)) |

◆ RCC_APB1ENR

| #define RCC_APB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x40)) |

◆ RCC_BASE

| #define RCC_BASE (AHB1PERIPH_BASE + 0x3800UL) |

◆ TIMEOUT

| #define TIMEOUT 1000000 |

Function Documentation

◆ bmp180_read_reg()

| uint8_t bmp180_read_reg | ( | uint8_t | reg | ) |

◆ bmp180_read_u16()

| uint16_t bmp180_read_u16 | ( | uint8_t | reg | ) |

◆ bmp180_write_reg()

| void bmp180_write_reg | ( | uint8_t | reg, |

| uint8_t | value ) |

◆ i2c1_init()

| void i2c1_init | ( | void | ) |

◆ i2c1_read_data_nack()

| uint8_t i2c1_read_data_nack | ( | void | ) |

◆ i2c1_start()

| void i2c1_start | ( | void | ) |

◆ i2c1_stop()

| void i2c1_stop | ( | void | ) |

◆ i2c1_write_addr()

| void i2c1_write_addr | ( | uint8_t | addr | ) |

◆ i2c1_write_data()

| void i2c1_write_data | ( | uint8_t | data | ) |

◆ main()

| int main | ( | void | ) |

◆ uart2_write_hex()

| void uart2_write_hex | ( | uint8_t | val | ) |

◆ uart2_write_uint16()

| void uart2_write_uint16 | ( | uint16_t | val | ) |

◆ wait_flag()

| int wait_flag | ( | volatile uint32_t * | reg, |

| uint32_t | mask ) |