Loading...

Searching...

No Matches

main.c File Reference

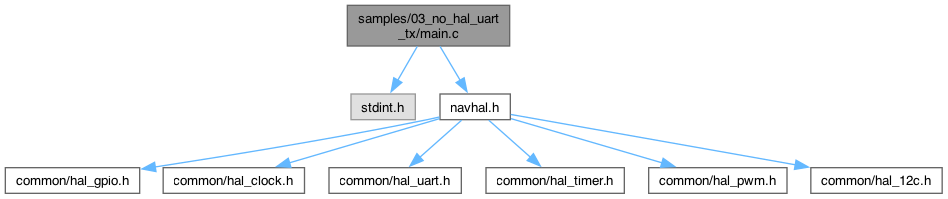

Include dependency graph for main.c:

Macros | |

| #define | CORTEX_M4 |

| #define | PERIPH_BASE 0x40000000UL |

| #define | AHB1PERIPH_BASE (PERIPH_BASE + 0x00020000UL) |

| #define | APB1PERIPH_BASE (PERIPH_BASE + 0x00000000UL) |

| #define | GPIOA_BASE (AHB1PERIPH_BASE + 0x0000) |

| #define | RCC_BASE (AHB1PERIPH_BASE + 0x3800) |

| #define | USART2_BASE (APB1PERIPH_BASE + 0x4400) |

| #define | RCC_AHB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x30)) |

| #define | RCC_APB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x40)) |

| #define | GPIOA_MODER (*(volatile uint32_t *)(GPIOA_BASE + 0x00)) |

| #define | GPIOA_AFRL (*(volatile uint32_t *)(GPIOA_BASE + 0x20)) |

| #define | USART2_SR (*(volatile uint32_t *)(USART2_BASE + 0x00)) |

| #define | USART2_DR (*(volatile uint32_t *)(USART2_BASE + 0x04)) |

| #define | USART2_BRR (*(volatile uint32_t *)(USART2_BASE + 0x08)) |

| #define | USART2_CR1 (*(volatile uint32_t *)(USART2_BASE + 0x0C)) |

| #define | RCC_AHB1ENR_GPIOAEN (1 << 0) |

| #define | RCC_APB1ENR_USART2EN (1 << 17) |

| #define | USART_CR1_UE (1 << 13) |

| #define | USART_CR1_TE (1 << 3) |

| #define | USART_SR_TXE (1 << 7) |

Functions | |

| void | delay (volatile uint32_t count) |

| void | uart2_init (void) |

| void | uart2_write_char (char c) |

| void | uart2_write_int (int num) |

| void | uart2_write_string (const char *s) |

| int | main (void) |

Variables | |

| hal_clock_config_t | clk_cfg |

| hal_pll_config_t | pll_cfg |

Macro Definition Documentation

◆ AHB1PERIPH_BASE

| #define AHB1PERIPH_BASE (PERIPH_BASE + 0x00020000UL) |

◆ APB1PERIPH_BASE

| #define APB1PERIPH_BASE (PERIPH_BASE + 0x00000000UL) |

◆ CORTEX_M4

| #define CORTEX_M4 |

◆ GPIOA_AFRL

| #define GPIOA_AFRL (*(volatile uint32_t *)(GPIOA_BASE + 0x20)) |

◆ GPIOA_BASE

| #define GPIOA_BASE (AHB1PERIPH_BASE + 0x0000) |

◆ GPIOA_MODER

| #define GPIOA_MODER (*(volatile uint32_t *)(GPIOA_BASE + 0x00)) |

◆ PERIPH_BASE

| #define PERIPH_BASE 0x40000000UL |

◆ RCC_AHB1ENR

| #define RCC_AHB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x30)) |

◆ RCC_AHB1ENR_GPIOAEN

| #define RCC_AHB1ENR_GPIOAEN (1 << 0) |

◆ RCC_APB1ENR

| #define RCC_APB1ENR (*(volatile uint32_t *)(RCC_BASE + 0x40)) |

◆ RCC_APB1ENR_USART2EN

| #define RCC_APB1ENR_USART2EN (1 << 17) |

◆ RCC_BASE

| #define RCC_BASE (AHB1PERIPH_BASE + 0x3800) |

◆ USART2_BASE

| #define USART2_BASE (APB1PERIPH_BASE + 0x4400) |

◆ USART2_BRR

| #define USART2_BRR (*(volatile uint32_t *)(USART2_BASE + 0x08)) |

◆ USART2_CR1

| #define USART2_CR1 (*(volatile uint32_t *)(USART2_BASE + 0x0C)) |

◆ USART2_DR

| #define USART2_DR (*(volatile uint32_t *)(USART2_BASE + 0x04)) |

◆ USART2_SR

| #define USART2_SR (*(volatile uint32_t *)(USART2_BASE + 0x00)) |

◆ USART_CR1_TE

| #define USART_CR1_TE (1 << 3) |

◆ USART_CR1_UE

| #define USART_CR1_UE (1 << 13) |

◆ USART_SR_TXE

| #define USART_SR_TXE (1 << 7) |

Function Documentation

◆ delay()

| void delay | ( | volatile uint32_t | count | ) |

◆ main()

| int main | ( | void | ) |

◆ uart2_init()

| void uart2_init | ( | void | ) |

◆ uart2_write_int()

| void uart2_write_int | ( | int | num | ) |

Variable Documentation

◆ clk_cfg

| hal_clock_config_t clk_cfg |

Initial value:

= {

@ HAL_CLOCK_SOURCE_PLL

Phase-locked loop (derived clock)

Definition clock_types.h:27

◆ pll_cfg

| hal_pll_config_t pll_cfg |

Initial value: