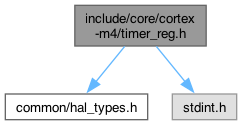

#include "common/hal_types.h"

#include <stdint.h>

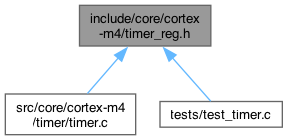

Go to the source code of this file.

◆ GPTIMx_BASE_ADDR

| #define GPTIMx_BASE_ADDR 0x40000000 |

◆ TIM1_BASE_ADDR

| #define TIM1_BASE_ADDR 0x40010000 |

◆ TIM2_5_ARR_MASK

| #define TIM2_5_ARR_MASK 0xFFFFFFFF |

◆ TIM2_5_CCRy_MASK

| #define TIM2_5_CCRy_MASK 0xFFFFFFFF |

◆ TIM2_5_CNT_MASK

| #define TIM2_5_CNT_MASK 0xFFFFFFFF |

◆ TIM9_BASE_ADDR

| #define TIM9_BASE_ADDR 0x40014000 |

◆ TIMx_ARR_MASK

| #define TIMx_ARR_MASK 0xFFFF |

◆ TIMx_CCER_CCxE_MASK

| #define TIMx_CCER_CCxE_MASK |

( |

| n | ) |

|

Value:(0x1 << (((n % 4) - 1) * 4))

◆ TIMx_CCMRy_OCxM_PWM_MODE2_MASK

| #define TIMx_CCMRy_OCxM_PWM_MODE2_MASK |

( |

| ch | ) |

|

Value:

#define TIMx_CCMRy_OCzM_Pos(ch)

Definition timer_reg.h:107

◆ TIMx_CCMRy_OCxPE

| #define TIMx_CCMRy_OCxPE |

( |

| ch | ) |

|

Value:

#define TIMx_CCMRy_OCzPE_Pos(ch)

Definition timer_reg.h:106

◆ TIMx_CCMRy_OCzM_MASK

| #define TIMx_CCMRy_OCzM_MASK |

( |

| ch | ) |

|

◆ TIMx_CCMRy_OCzM_Pos

| #define TIMx_CCMRy_OCzM_Pos |

( |

| ch | ) |

|

Value:((ch % 2 == 1) ? 0x4 : 0x12)

◆ TIMx_CCMRy_OCzM_PWM_MODE1_MASK

| #define TIMx_CCMRy_OCzM_PWM_MODE1_MASK |

( |

| ch | ) |

|

◆ TIMx_CCMRy_OCzPE_Pos

| #define TIMx_CCMRy_OCzPE_Pos |

( |

| ch | ) |

|

Value:((ch % 2 == 1) ? 0x3 : 0x11)

◆ TIMx_CCRy_MASK

| #define TIMx_CCRy_MASK 0xFFFF |

◆ TIMx_CNT_MASK

| #define TIMx_CNT_MASK 0xFFFF |

◆ TIMx_CR1_CEN

◆ TIMx_DIER_UIE

| #define TIMx_DIER_UIE 0x1 |

◆ TIMx_EGR_UG

◆ TIMx_PSC_MASK

| #define TIMx_PSC_MASK 0xFFFF |

◆ TIMx_SR_UIF