Loading...

Searching...

No Matches

interrupt_reg.h File Reference

Cortex-M4 NVIC (Nested Vector Interrupt Controller) register definitions. More...

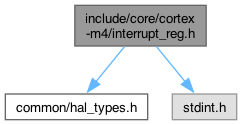

Include dependency graph for interrupt_reg.h:

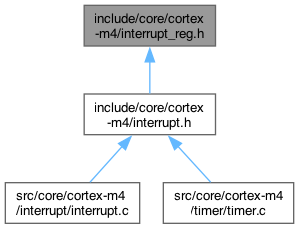

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | NVIC_Typedef |

| NVIC register map. More... | |

Macros | |

| #define | NVIC_BASE_ADDR 0xE000E100UL |

| #define | NVIC ((NVIC_Typedef *)NVIC_BASE_ADDR) |

Detailed Description

Cortex-M4 NVIC (Nested Vector Interrupt Controller) register definitions.

This header defines the memory-mapped structure for NVIC registers, including set-enable, clear-enable, set-pending, clear-pending, active bit, and priority registers. It also enumerates all Cortex-M4 processor exceptions and STM32F4-specific interrupt numbers for use in HAL and driver code.

- Note

- The NVIC base address is 0xE000E100UL.

- Copyright

- © NAVROBOTEC PVT. LTD.

Macro Definition Documentation

◆ NVIC

| #define NVIC ((NVIC_Typedef *)NVIC_BASE_ADDR) |

NVIC instance pointer

◆ NVIC_BASE_ADDR

| #define NVIC_BASE_ADDR 0xE000E100UL |

NVIC base address

Enumeration Type Documentation

◆ IRQn_Type

| enum IRQn_Type |

Cortex-M4 and STM32F4 interrupt numbers.

Enumerates processor exceptions and STM32F4-specific peripheral interrupts for use in configuring NVIC and enabling/disabling interrupts.