Loading...

Searching...

No Matches

gpio_reg.h File Reference

Cortex-M4 GPIO register definitions and access macros. More...

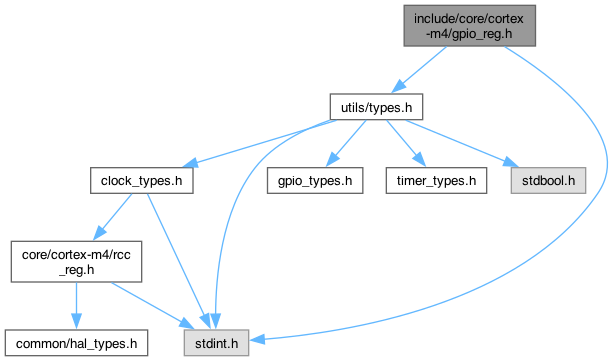

Include dependency graph for gpio_reg.h:

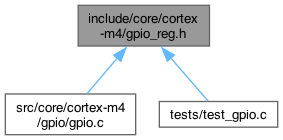

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Classes | |

| struct | GPIOx_Typedef |

| GPIO port register structure. More... | |

Macros | |

| #define | GPIOA_BASE_ADDR 0x40020000 |

| #define | GPIOB_BASE_ADDR 0x40020400 |

| #define | GPIOC_BASE_ADDR 0x40020800 |

| #define | GPIOD_BASE_ADDR 0x40020C00 |

| #define | GPIOE_BASE_ADDR 0x40021000 |

| #define | GPIOH_BASE_ADDR 0x40021C00 |

| #define | GPIO_GET_PORT_NUMBER(n) |

| #define | GPIO_GET_PORT(n) |

| #define | GPIO_GET_PIN(n) |

Detailed Description

Cortex-M4 GPIO register definitions and access macros.

This header defines the GPIO register structure and macros to access GPIO ports and pins on Cortex-M4 microcontrollers.

Structures:

- GPIOx_Typedef : Represents the memory-mapped GPIO registers for a port.

Macros:

- GPIOA_BASE_ADDR to GPIOH_BASE_ADDR : Base addresses of GPIO ports.

- GPIO_GET_PORT_NUMBER(n) : Compute the port number from a pin number.

- GPIO_GET_PORT(n) : Get a pointer to the GPIO port structure.

- GPIO_GET_PIN(n) : Get the pin number within a port.

- Copyright

- © NAVROBOTEC PVT. LTD.

Macro Definition Documentation

◆ GPIO_GET_PIN

| #define GPIO_GET_PIN | ( | n | ) |

Value:

(n % 16)

Get pin number within the port from absolute pin number

◆ GPIO_GET_PORT

| #define GPIO_GET_PORT | ( | n | ) |

Value:

Get pointer to GPIO port structure from absolute pin number

◆ GPIO_GET_PORT_NUMBER

| #define GPIO_GET_PORT_NUMBER | ( | n | ) |

Value:

(n / 16 == 5 ? 7 : n / 16)

Get port number from absolute pin number

◆ GPIOA_BASE_ADDR

| #define GPIOA_BASE_ADDR 0x40020000 |

Base addresses for GPIO ports GPIOA base address

◆ GPIOB_BASE_ADDR

| #define GPIOB_BASE_ADDR 0x40020400 |

GPIOB base address

◆ GPIOC_BASE_ADDR

| #define GPIOC_BASE_ADDR 0x40020800 |

GPIOC base address

◆ GPIOD_BASE_ADDR

| #define GPIOD_BASE_ADDR 0x40020C00 |

GPIOD base address

◆ GPIOE_BASE_ADDR

| #define GPIOE_BASE_ADDR 0x40021000 |

GPIOE base address

◆ GPIOH_BASE_ADDR

| #define GPIOH_BASE_ADDR 0x40021C00 |

GPIOH base address