Cortex-M4 specific clock control HAL interface. More...

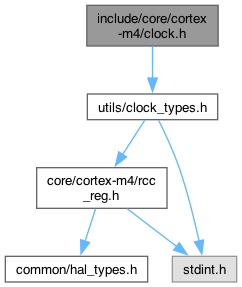

#include "utils/clock_types.h"

Go to the source code of this file.

Classes | |

| struct | hal_pll_config_t |

| PLL (Phase Locked Loop) configuration structure. More... | |

Functions | |

| void | hal_clock_init (hal_clock_config_t *cfg, hal_pll_config_t *pll_cfg) |

| Initialize the system clock. | |

| uint32_t | hal_clock_get_sysclk (void) |

| Get the system clock frequency (SYSCLK). | |

| uint32_t | hal_clock_get_ahbclk (void) |

| Get the AHB bus clock frequency. | |

| uint32_t | hal_clock_get_apb1clk (void) |

| Get the APB1 bus clock frequency. | |

| uint32_t | hal_clock_get_apb2clk (void) |

| Get the APB2 bus clock frequency. | |

Detailed Description

Cortex-M4 specific clock control HAL interface.

This header defines the structures and functions to configure and query the system and peripheral clocks for Cortex-M4 microcontrollers. It includes PLL configuration, system clock initialization, and AHB/APB clock retrieval functions.

The HAL provides a platform-independent abstraction while leveraging the Cortex-M4 specific hardware.

- Copyright

- © NAVROBOTEC PVT. LTD.

Function Documentation

◆ hal_clock_get_ahbclk()

| uint32_t hal_clock_get_ahbclk | ( | void | ) |

Get the AHB bus clock frequency.

- Returns

- AHB clock frequency in Hz.

Get the AHB bus clock frequency.

- Returns

- AHB clock frequency in Hz

◆ hal_clock_get_apb1clk()

| uint32_t hal_clock_get_apb1clk | ( | void | ) |

Get the APB1 bus clock frequency.

- Returns

- APB1 clock frequency in Hz.

Get the APB1 bus clock frequency.

- Returns

- APB1 clock frequency in Hz

◆ hal_clock_get_apb2clk()

| uint32_t hal_clock_get_apb2clk | ( | void | ) |

Get the APB2 bus clock frequency.

- Returns

- APB2 clock frequency in Hz.

Get the APB2 bus clock frequency.

- Returns

- APB2 clock frequency in Hz

◆ hal_clock_get_sysclk()

| uint32_t hal_clock_get_sysclk | ( | void | ) |

Get the system clock frequency (SYSCLK).

- Returns

- System clock frequency in Hz.

Get the system clock frequency (SYSCLK).

- Returns

- SYSCLK frequency in Hz

Determines SYSCLK frequency based on current clock source:

- HSI: Fixed 16 MHz

- HSE: Fixed 8 MHz

- PLL: Calculated from PLL configuration registers

◆ hal_clock_init()

| void hal_clock_init | ( | hal_clock_config_t * | cfg, |

| hal_pll_config_t * | pll_cfg ) |

Initialize the system clock.

- Parameters

-

cfg Pointer to the main clock configuration structure. pll_cfg Pointer to the PLL configuration structure.

- Note

- This function must be called before using other peripheral clocks.

Initialize the system clock.

- Parameters

-

[in] cfg Pointer to clock configuration structure [in] pll_cfg Pointer to PLL configuration structure (required if using PLL)

Configures the complete clock tree including:

- Clock source selection (HSI/HSE/PLL)

- PLL configuration (when used)

- Flash latency settings

- AHB/APB prescalers

- Note

- This function will block until clock switches are complete

< Flash Interface base address

< Flash ACR Latency bit position

< Flash ACR Latency bit position