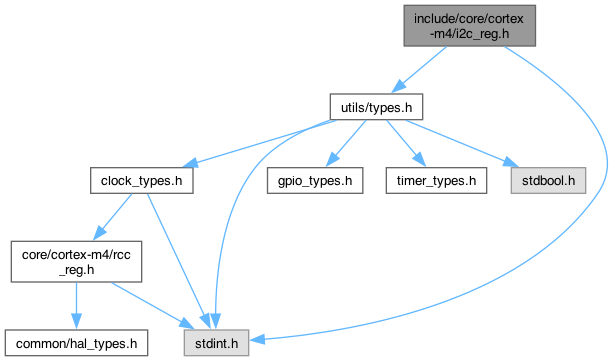

Cortex-M4 I²C peripheral register definitions and bit masks. More...

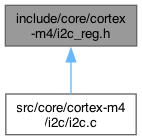

Go to the source code of this file.

Classes | |

| struct | I2C_Reg_Typedef |

| I²C peripheral register map. More... | |

Detailed Description

Cortex-M4 I²C peripheral register definitions and bit masks.

This header defines the memory-mapped structure of I²C registers and related macros for accessing and configuring the I²C peripheral on Cortex-M4 microcontrollers.

Structures:

- I2C_Reg_Typedef : Represents the layout of I²C registers.

Macros:

- Base addresses and port access macros.

- Control (CR1, CR2), status (SR1, SR2), clock (CCR, TRISE), and filter (FLTR) bits.

These definitions allow the HAL and driver code to manipulate I²C hardware registers in a readable and maintainable way.

- Copyright

- © NAVROBOTEC PVT. LTD.

Macro Definition Documentation

◆ I2C_APB1ENR_MASK

| #define I2C_APB1ENR_MASK | ( | n | ) |

Enable mask for APB1 peripheral clock

◆ I2C_BASE_ADDR

| #define I2C_BASE_ADDR 0x40005400 |

Base address for I²C peripheral I²C base address

◆ I2C_CCR_CCR_MASK

| #define I2C_CCR_CCR_MASK (0xFFFU << I2C_CCR_CCR_Pos) |

◆ I2C_CCR_CCR_Pos

| #define I2C_CCR_CCR_Pos 0 |

CCR register bit positions and masks

◆ I2C_CCR_DUTY

| #define I2C_CCR_DUTY (1U << I2C_CCR_DUTY_Pos) |

◆ I2C_CCR_DUTY_Pos

| #define I2C_CCR_DUTY_Pos 14 |

◆ I2C_CCR_FS_MASK

| #define I2C_CCR_FS_MASK (1U << I2C_CCR_FS_Pos) |

◆ I2C_CCR_FS_Pos

| #define I2C_CCR_FS_Pos 15 |

◆ I2C_CR1_ACK_MASK

| #define I2C_CR1_ACK_MASK (1U << I2C_CR1_ACK_Pos) |

◆ I2C_CR1_ACK_Pos

| #define I2C_CR1_ACK_Pos 10 |

◆ I2C_CR1_PE_MASK

| #define I2C_CR1_PE_MASK (1U << I2C_CR1_PE_Pos) |

◆ I2C_CR1_PE_Pos

| #define I2C_CR1_PE_Pos 0 |

CR1 register bit positions and masks

◆ I2C_CR1_POS_MASK

| #define I2C_CR1_POS_MASK (1U << I2C_CR1_POS_Pos) |

◆ I2C_CR1_POS_Pos

| #define I2C_CR1_POS_Pos 11 |

◆ I2C_CR1_START_MASK

| #define I2C_CR1_START_MASK (1U << I2C_CR1_START_Pos) |

◆ I2C_CR1_START_Pos

| #define I2C_CR1_START_Pos 8 |

◆ I2C_CR1_STOP_MASK

| #define I2C_CR1_STOP_MASK (1U << I2C_CR1_STOP_Pos) |

◆ I2C_CR1_STOP_Pos

| #define I2C_CR1_STOP_Pos 9 |

◆ I2C_CR1_SWRST_MASK

| #define I2C_CR1_SWRST_MASK (1U << I2C_CR1_SWRST_Pos) |

◆ I2C_CR1_SWRST_Pos

| #define I2C_CR1_SWRST_Pos 15 |

◆ I2C_CR2_FREQ_MASK

| #define I2C_CR2_FREQ_MASK (0x3FU << I2C_CR2_FREQ_Pos) |

◆ I2C_CR2_FREQ_Pos

| #define I2C_CR2_FREQ_Pos 0 |

CR2 register bit positions and masks

◆ I2C_CR2_ITBUFEN

| #define I2C_CR2_ITBUFEN (1U << I2C_CR2_ITBUFEN_Pos) |

◆ I2C_CR2_ITBUFEN_Pos

| #define I2C_CR2_ITBUFEN_Pos 10 |

◆ I2C_CR2_ITERREN

| #define I2C_CR2_ITERREN (1U << I2C_CR2_ITERREN_Pos) |

◆ I2C_CR2_ITERREN_Pos

| #define I2C_CR2_ITERREN_Pos 8 |

◆ I2C_CR2_ITEVTEN

| #define I2C_CR2_ITEVTEN (1U << I2C_CR2_ITEVTEN_Pos) |

◆ I2C_CR2_ITEVTEN_Pos

| #define I2C_CR2_ITEVTEN_Pos 9 |

◆ I2C_GET_BASE

| #define I2C_GET_BASE | ( | n | ) |

Get pointer to I²C peripheral instance

◆ I2C_SR1_ADDR_MASK

| #define I2C_SR1_ADDR_MASK (1U << I2C_SR1_ADDR_Pos) |

◆ I2C_SR1_ADDR_Pos

| #define I2C_SR1_ADDR_Pos 1 |

◆ I2C_SR1_AF

| #define I2C_SR1_AF (1U << I2C_SR1_AF_Pos) |

◆ I2C_SR1_AF_Pos

| #define I2C_SR1_AF_Pos 10 |

◆ I2C_SR1_ARLO

| #define I2C_SR1_ARLO (1U << I2C_SR1_ARLO_Pos) |

◆ I2C_SR1_ARLO_Pos

| #define I2C_SR1_ARLO_Pos 9 |

◆ I2C_SR1_BERR

| #define I2C_SR1_BERR (1U << I2C_SR1_BERR_Pos) |

◆ I2C_SR1_BERR_Pos

| #define I2C_SR1_BERR_Pos 8 |

◆ I2C_SR1_BTF_MASK

| #define I2C_SR1_BTF_MASK (1U << I2C_SR1_BTF_Pos) |

◆ I2C_SR1_BTF_Pos

| #define I2C_SR1_BTF_Pos 2 |

◆ I2C_SR1_OVR

| #define I2C_SR1_OVR (1U << I2C_SR1_OVR_Pos) |

◆ I2C_SR1_OVR_Pos

| #define I2C_SR1_OVR_Pos 11 |

◆ I2C_SR1_RXNE_MASK

| #define I2C_SR1_RXNE_MASK (1U << I2C_SR1_RXNE_Pos) |

◆ I2C_SR1_RXNE_Pos

| #define I2C_SR1_RXNE_Pos 6 |

◆ I2C_SR1_SB_MASK

| #define I2C_SR1_SB_MASK (1U << I2C_SR1_SB_Pos) |

◆ I2C_SR1_SB_Pos

| #define I2C_SR1_SB_Pos 0 |

SR1 register bit positions and masks

◆ I2C_SR1_STOPF

| #define I2C_SR1_STOPF (1U << I2C_SR1_STOPF_Pos) |

◆ I2C_SR1_STOPF_Pos

| #define I2C_SR1_STOPF_Pos 4 |

◆ I2C_SR1_TIMEOUT

| #define I2C_SR1_TIMEOUT (1U << I2C_SR1_TIMEOUT_Pos) |

◆ I2C_SR1_TIMEOUT_Pos

| #define I2C_SR1_TIMEOUT_Pos 14 |

◆ I2C_SR1_TXE_MASK

| #define I2C_SR1_TXE_MASK (1U << I2C_SR1_TXE_Pos) |

◆ I2C_SR1_TXE_Pos

| #define I2C_SR1_TXE_Pos 7 |

◆ I2C_SR2_BUSY

| #define I2C_SR2_BUSY (1U << I2C_SR2_BUSY_Pos) |

◆ I2C_SR2_BUSY_Pos

| #define I2C_SR2_BUSY_Pos 1 |

◆ I2C_SR2_MSL

| #define I2C_SR2_MSL (1U << I2C_SR2_MSL_Pos) |

◆ I2C_SR2_MSL_Pos

| #define I2C_SR2_MSL_Pos 0 |

SR2 register bit positions

◆ I2C_SR2_TRA

| #define I2C_SR2_TRA (1U << I2C_SR2_TRA_Pos) |

◆ I2C_SR2_TRA_Pos

| #define I2C_SR2_TRA_Pos 2 |

◆ I2C_TRISE_TRISE_Msk

| #define I2C_TRISE_TRISE_Msk (0x3FU << I2C_TRISE_TRISE_Pos) |

◆ I2C_TRISE_TRISE_Pos

| #define I2C_TRISE_TRISE_Pos 0 |

TRISE register bit positions and masks